81

Constants And Data Structures

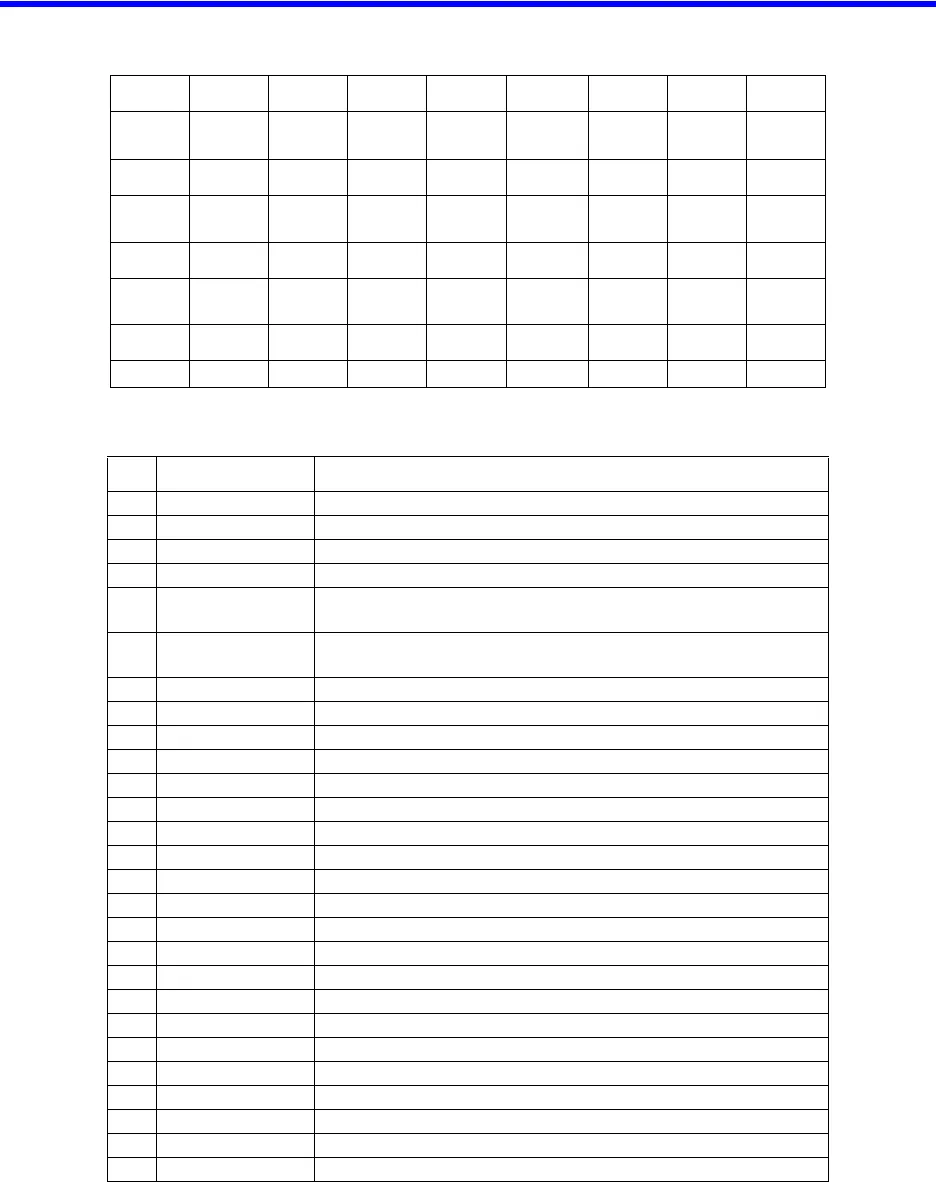

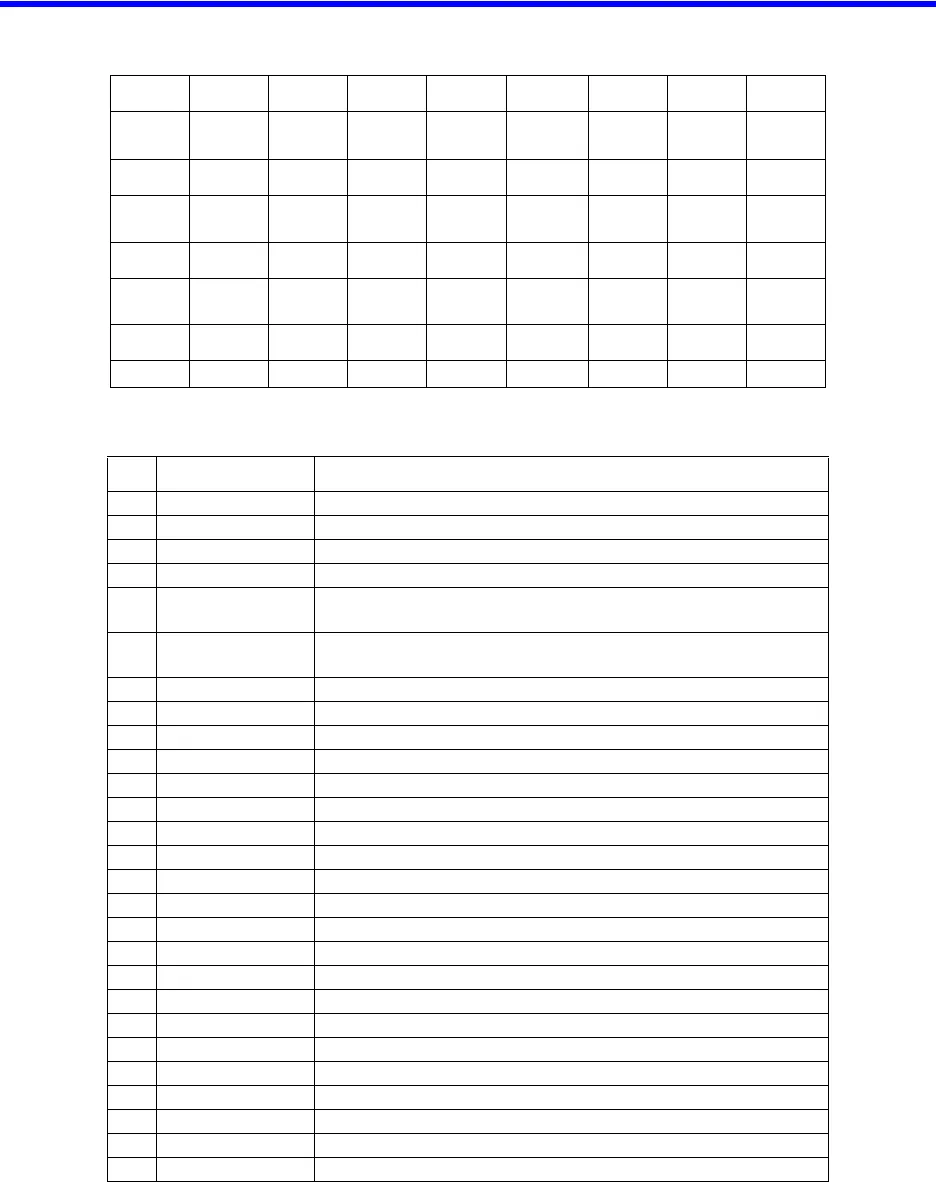

Table 5-63 BDS System Status Bitfield

Note: If all bits are 0, then all is well – no status to report.

Note: Status bitfield descriptions – describes the state when the bit is set (1).

Bit3130292827262524

DSP Unit DSP

ERR

DCM3 DCM2 DCM1 DCM0 PLL12 PLL8

Bit2322212019181716

XXArc

Detected

Not Cal Probe

Disconnect

I Over V Over I Low

Bit151413121110 9 8

V Low F5

Range

F4

Range

F3

Range

F2 Range F1

Range

DAQ

Timeout

No Time

Set

Bit76543210

XXXXAGC OffDeembedAvgIdle

Bit Name Description

0 Idle The BDS is in the Idle Run Mode. Not running or collecting any data.

1 Avg Data averaging enabled.

2 De-embed Measurement de-embedding enabled.

3 AGC Off Auto gain control disabled.

8 No Time Set The Date and Time attribute of the BDS Host Configuration

class has not been set.

9 DAQ Timeout Data acquisition timeout – data not produced in the time

requested.

10 F1 Range Frequency 1 range error.

11 F2 Range Frequency 2 range error.

12 F3 Range Frequency 3 range error.

13 F4 Range Frequency 4 range error.

14 F5 Range Frequency 5 range error.

15 V Low Low voltage signal warning.

16 I Low Low current signal warning.

17 V Over Over range detected on the Voltage channel.

18 I Over Over range detected on the Current channel.

19 Probe Disconnect The BDS probe has been disconnected from the receiver box.

20 Not Cal Data not calibrated.

21 Arc Detected Arc transient event detected.

24 PLL8 8-bit PLL lock error.

25 PLL12 12-bit PLL lock error.

26 DCM0 DCM (Digital Clock Manager) 0 lock lost.

27 DCM1 DCM (Digital Clock Manager) 1 lock lost.

28 DCM2 DCM (Digital Clock Manager) 2 lock lost.

29 DCM3 DCM (Digital Clock Manager) 3 lock lost.

30 DSP ERR DSP/FPGA internal error.

31 DSP Init DSP/FPGA initialization error.

X Bit reserved for future use.